Innovation for the next generation

# ML4039EML

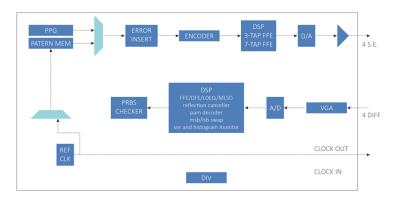

4-Channel | 56 Gbaud PAM4 & NRZ | Bit Error Ratio Tester 400G | Integrated EML Laser Driver |

SSPRQ, PRBS13Q & PRBS31Q | TX and RX Equalizers | Signal SNR and Histogram | High Voltage Amplitude |

## Summary

With the accelerated growth of hyperscale datacenters, the performance demands on Ethernet network infrastructure is increasing exponentially, and customer expectations for high-speed data throughput is at an all-time high. As a result, Bit Error Rate Testers (BERT) have become a cornerstone for physical layer testing, from qualifying bit transmission for fiber optic and copper-wire digital data transmission lines to testing signal integrity.

A BERT generates a sequence of bits through a communication channel and the received bits are then compared against the transmitted bits. A Bit Error Ratio (BER) evaluates the full end-to-end performance of a connectivity system and assures communication reliability.

## **ML4039EML**

#### 4x 56 GBd BERT

#### Introduction

The ML4039EML is a full featuree 400G BERT that can be configured as a four-channel PAM4 56 GBaud or four-channel NRZ 56 Gbps lanes. Also, half rates around 28 GBd are supported.

The transmitters Support all standard test patterns mandated by IEEE and OIF such as PRBS13Q, SSPRQ, PRBS31Q, etc...

It is also possible to program the TX to output a user-defined pattern of 16384 UI maximum size The transmitters are single-ended with swing up to 1800 mVpp to enable driving EML-based optics.

The error detectors are differential pairs with adaptive front-end signal conditioning.

#### **Key Features**

#### **Transmit:**

Data Rates: 23 – 29 & 46 – 58 Gbps Ability to tune the bit rate in steps of 100 kbps and find the RX PLL locking margin. Independent control of inner eye levels Up to 1.8 Vpp output swing single ended supports Gray coding and polarity inversion

#### Available patterns are:

- PRBS 7/9/11/13/15/16/23/31/58 and their inverses

- PRBS13Q, PRBS31Q

- SSPRQ

- Square wave

- Error injection

3-tap LUT-based Pre- and Post-emphasis

7-tap linear FFE-based de-emphasis

#### Receive:

Adaptive DFE and FFE with reflection canceller and MLSD.

AGC

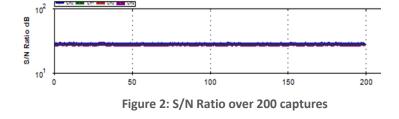

SNR monitoring over time.

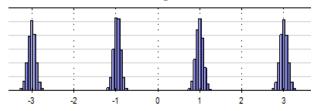

PAM histogram monitor.

PAM slicer threshold adjustable.

#### **Error-detection on following patterns:**

- PRBS 7/9/11/15/16/23/31

- PRBS13Q and PRBS31Q

LOS indicators

Adaptive 10-tap FFE monitor

#### **General:**

API libraries with documentation. LabView driver and Python wrapper available. Same product available in ATE format for Verigy 93K and Teradyne.

## **Target Applications**

Production testing of transceiver drivers and TIAs.

Functional and SI testing.

Figure 1: PAM eye histogram

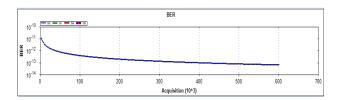

Figure 3: BER curves for one channel with 1 error inserted at the MSB and LSB respectively

## **Electrical Specifications**

| Parameter                             | Specifications                                                     |

|---------------------------------------|--------------------------------------------------------------------|

| Bit Rates                             | 23 – 29 GBaud and 46 – 58 GBaud                                    |

| TX Amplitude                          | 0 - 1800 mV                                                        |

| Patterns                              | PRBS 7/9/11/13/15/16/23/31/58 - PRBS13Q, 31Q and SSPRQ Square wave |

| TX Amplitude Adjustment               | Steps of 1 mV                                                      |

| Pre- / Post-emphasis                  | 6 dB                                                               |

| Pre-Emphasis Resolution               | 1000 steps                                                         |

| Equalizing Filter Spacing             | 101                                                                |

| Random Jitter RMS                     | 230 fs                                                             |

| Rise/ Fall Time (20–80%) <sup>1</sup> | 10 ps                                                              |

| Coding                                | DFE Pre-coding and Gray coding supported                           |

| Output Return Loss up to 10GHz        | <-15dB                                                             |

| Output Return Loss (16-25GHz)         | <-10dB                                                             |

| Error Detector input range            | 50 mV- 800 mV diff.                                                |

$<sup>^{\</sup>rm 1}$  With appropriate pre and post emphasis settings and 50 GHz scope

| Total DFE/FFE/CTLE Equalization  | Up to 13 dB                                                    |

|----------------------------------|----------------------------------------------------------------|

| Error-detector VGA dynamic range | ± 2 dB                                                         |

| TX/RX connectors                 | 2.92 mm or 2.4 mm Connectors                                   |

| Reference clock Output           | Rate div 16/32/128/256                                         |

| Diff. Input Return Loss          | Better than 10 dB                                              |

| Histogram                        | 160 levels. Reports Counts/level based on 2 <sup>20</sup> bits |

| Clock Input Range                | Up to 4.4 GHz                                                  |

| Clock Input Amplitude            | 200 - 1000 mV                                                  |

| Input Impedance                  | 50 Ω                                                           |

| Temperature range                | 0-75 °C                                                        |

| Power                            | 110V, 1.4A or 220V, 0.9A – 50/60 Hz                            |

| Power (ATE version only)         | 12 V, 1.5A                                                     |

| PRBS Pattern | Polynomial                 |

|--------------|----------------------------|

| 7            | x^7 + x^6 + 1              |

| 9 variant 1  | x^9 + x^4 + 1              |

| 9 variant 2  | x^9 + x^5 + 1              |

| 11           | x^11 + x^9 + 1             |

| 13Q          | x^13 + x^12 + x^2 + x + 1  |

| 15           | x^15 + x^4 + 1             |

| 16           | x^16 + x^5 + x^3 + x^2 + 1 |

| 23           | x^23 + x^18 + 1            |

| 31           | x^31 + x^28 + 1            |

| 58           | x^58 + x^39 + 1            |

#### **Mechanical Dimensions**

The ML4039EML is a benchtop instrument that fits in a 19-inch 2U rack. TwoBERTs arranged side by side comprise one 2U slot in the rack. Multilane supplies the needed brackets.

### **Ordering Information**

Please contact us at <a href="mailto:sales@multilaneinc.com">sales@multilaneinc.com</a>.

#### **North America**

48521 Warm Springs Boulevard Suite 310 Fremont, CA 94539, USA +1 510 573 6388

#### Worldwide

Houmal Technology Park Askarieh Main Road Houmal, Lebanon +961 5 941 668

#### Asia

14F-5/ Rm.5, 14F., No 295 Sec.2, Guangfu Rd. East Dist., Hsinchu City 300, Taiwan (R.O.C) +886 3 5744 591